8 Minutės

Apple ir Qualcomm tyliai parodė susidomėjimą Intel pažangiomis pakavimo technologijomis, remiantis neseniai paskelbtais darbo pasiūlymais. Kai lustų dizaineriai ieško būdų padidinti našumą ir talpą, Intel EMIB ir Foveros sulaukia vis daugiau dėmesio — ir šis susidomėjimas gali pakeisti konkurencinę pažangaus pakavimo ir foundry paslaugų aplinką.

Kodėl didžiosios technologijų įmonės žvelgia už Moore’o dėsio ribų

Moore’o dėsnis nebeužtikrina tų pačių lengvų našumo ir tankio augimo etapų, kokius matėme anksčiau, todėl pramonė vis labiau remiasi pažangiu pakavimu (advanced packaging), kad sluoksniuotų, sujungtų ir išplėstų lustus viename pakete. Pažangios pakavimo technologijos, leidžiančios sujungti kelis chiplet elementus arba sluoksniuoti die sluoksnius, tapo kertinėmis aukštos klasės skaičiavimo (HPC) ir specializuotų silicio sprendimų dalimis, naudojamomis tokių gamintojų kaip Nvidia, AMD, taip pat Apple ir Qualcomm vidaus skaitmeninių lustų komandų darbams.

Tokios technologijos padeda išspręsti kritinius dizaino iššūkius: padidinti atminties pralaidumą, mažinti signalo vėlavimą, gerinti energijos efektyvumą ir pagerinti modulinumą, kai projektai yra sudėtingi ir apima skirtingus proceso mazgus. Heterogeninė integracija, kurioje loģika, atmintis, I/O ir specializuoti akceleratoriai derinami per pažangų pakavimą, tapo strateginiu resursu siekiant išlaikyti konkurencinį pranašumą, net kai tranzistorių tankis augti lėčiau.

Per pastaruosius metus TSMC dominavo šiame segmente su sprendimais, tokiais kaip CoWoS (Chip on Wafer on Substrate), tačiau didėjanti apetitas iš pagrindinių GPU ir CPU užsakovų sukėlė talpos įtampą. Ši klinika kūrė langą alternatyviems tiekėjams ir gamybos partneriams — ir Intel bando užpildyti šią spragą, siūlydama savo EMIB ir Foveros pakavimo platformas tiek vidaus poreikiams, tiek išoriniams klientams per foundry ir pakavimo paslaugas.

EMIB ir Foveros: dvi skirtingos kryptys tankesniems lustams

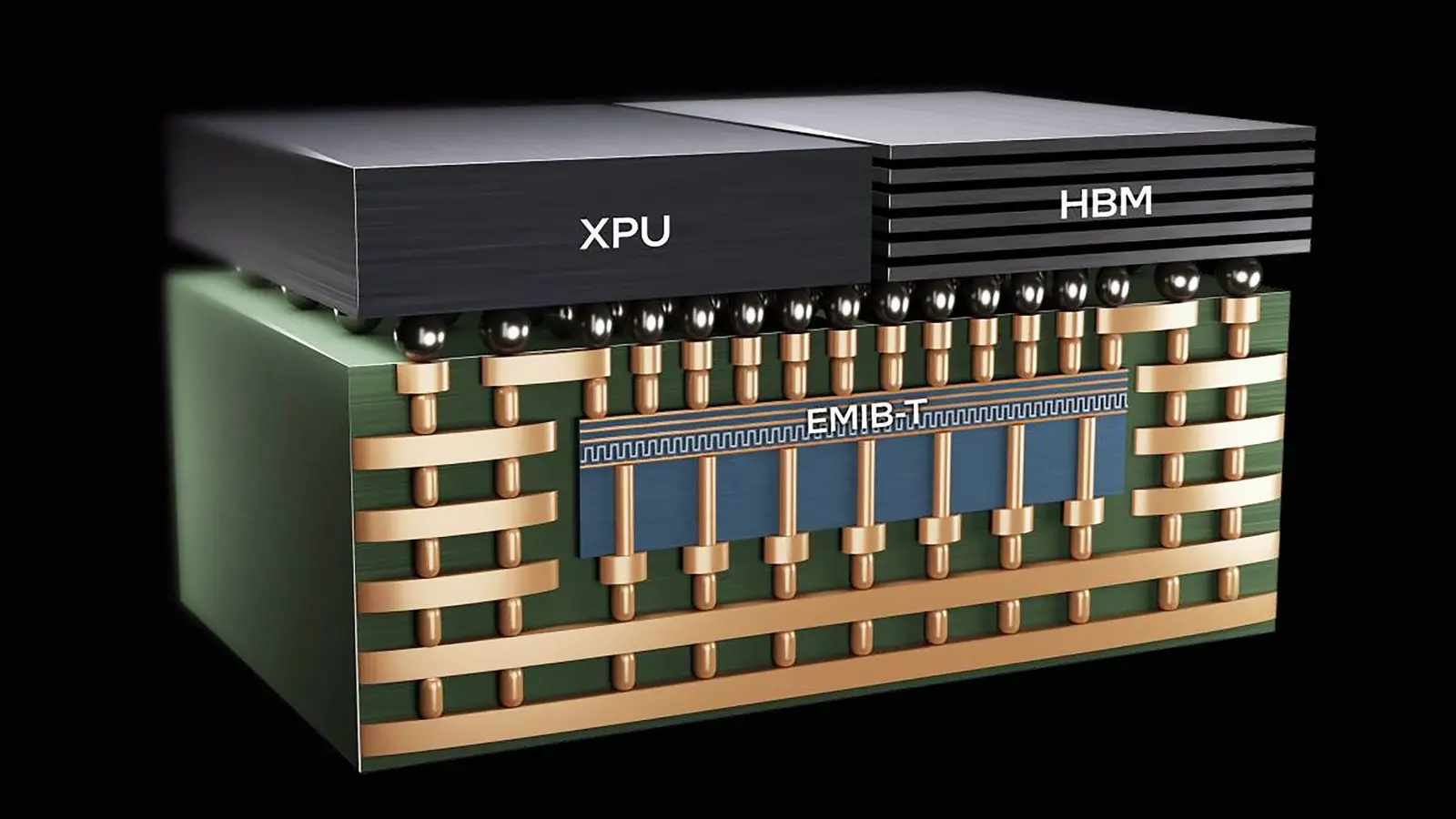

Intel EMIB (Embedded Multi-Die Interconnect Bridge) naudoja smulkius silicio tiltelius, kad sujungtų kelis chiplet’us viename pakete be didelio interposer’io. Tai leidžia sumažinti kainą ir didina dizaino lankstumą daugiasluoksniuose dizainuose. EMIB sprendimas ypač naudingas, kai reikia sujungti kelis die, pagamintus skirtingais proceso mazgais, arba integruoti HBM atmintį ar specialius IO blokelius be didelių tarpinio sluoksnio kaštų.

Techninė EMIB stiprybė yra jos gebėjimas derinti aukštos pralaidumo jungtis per trumpus signalo kelius, sumažinti interposer’io dydį ir pagerinti galutinio paketo terminius parametrus. Be to, EMIB gali supaprastinti testavimą ir gerinti derinimo galimybes, nes chiplet’ai gali būti gaminami atskirai ir vėliau sujungiami į galutinį paketą.

Foveros naudoja papildomą, dažnai priešingą požiūrį — tai die sluoksniavimo technologija. Naudodama per silicio vias (TSV, through-silicon vias) ir smulkų vertikalų integracijos žingsnį (fine-pitch vertical integration), Foveros leidžia dizaineriams vienas ant kito sluoksniuoti logiką ir atmintį, pasiekiant tankesnę integraciją, trumpesnius signalo kelius ir mažesnę latenciją tarp komponentų. Tokia vertikali integracija ypač vertinga, kai reikalingas itin greitas ryšys tarp procesoriaus branduolio ir atminties blokų arba tarp specializuotos akceleracijos logikos ir HBM tipo atminties.

Abu metodai — EMIB ir Foveros — turi savo privalumų ir kompromisų. EMIB paprastai suteikia daugiau dizaino lankstumo ir gali būti ekonomiškesnis projektams, kuriuose reikia daug įvairių die, tačiau ne taip intensyviai sluoksniuoti. Foveros leidžia pasiekti itin didelę integracijos tankumą ir labai trumpą tarpkomponentinę latenciją, bet iššaukiami technologiniai reikalavimai, tokie kaip terminis valdymas, TSV gamybos sudėtingumas ir tarpinių sluoksnių sąnaudos, gali didinti galutinę produkto kainą ir sudėtingumą.

Įmonėms, kurios siekia heterogeninės integracijos privalumų, bet nenori būti visiškai priklausomos nuo vieno foundry pakavimo kelio, šios Intel technologijos pasiūlo alternatyvų ekosistemą. Tai ypač svarbu projektams, kuriuose reikalingas optimizuotas HBM integravimas, panaudojamas aukštos spartos skaičiavimo užduotims, arba kur reikia įvairių IP blokų jungčių iš skirtingų proceso tiekėjų.

Užuominos iš personalo paieškos: Apple ir Qualcomm darbo skelbimai

Neseniai nutekėję arba viešinti darbo skelbimai iš Apple ir Qualcomm minima patirtis su Intel EMIB ir kitomis pakavimo technologijomis. Apple darbo pasiūlymas DRAM pakavimo inžinieriui nurodo reikalaujamas žinias apie CoWoS, EMIB, SoIC ir PoP. Qualcomm skelbimus apie produkto valdymo direktorių duomenų centrų skyriuje taip pat pažymi EMIB susipažinimo reikalavimą.

Tokių darbo skelbimų skaitymas reikalauja atidaus interpretavimo: jie negarantuoja iškart sudarytų komercinių sutarčių su Intel, bet aiškiai rodo, kad inžinerinės komandos aktyviai vertina ar eksperimentuoja su Intel pakavimo sprendimais. Kai dvi pramonės sunkiasvorės kompanijos atvirai ieško žinių apie tą pačią technologinę platformą, tai signalizuoja ne tik atsitiktinį susidomėjimą, bet ir sistemingą galimybės įvertinimą strateginiam partnerystės ar tiekimo diversifikavimo lygiui.

Darbo skelbimai dažnai atspindi ateities prioritetus: jie gali būti susiję su prototipų kūrimo etapais, planuojamais testavimo projektais ar numatomu gamybos perorientavimu į alternatyvius pakavimo tiekėjus. Tokie signalai yra ypač vertingi tiek konkurentams, tiek tiekimo grandinės analitikams, nes leidžia nuspėti, kuriomis technologijomis pasitiki dizaineriai ir kam jie gali patikėti kritines pakavimo grandis.

Ką tai gali reikšti foundry rinkai

Jei Apple, Qualcomm ar kiti didieji dizaineriai pasirinktų Intel pažangų pakavimą, pasekmės būtų reikšmingos. Pirma, tai patvirtintų, kad Intel ekosistema yra pakankamai subrendusi, kad palaikytų pažangiausių, pritaikytų silicio (custom silicon) programų poreikius. Antra, tai sumažintų spaudimą TSMC pažangaus pakavimo linijoms, suteikiant dizaineriams didesnę derybinę galią, lankstumą planavime ir potencialiai geresnes kainodaros galimybes.

Rinkos diversifikacija taip pat gali sumažinti riziką tiekimo grandinėje: jeigu vienas tiekėjas susiduria su vėlavimais ar prioritetų keitimais (pvz., TSMC prioritetizuoja didelio apimto GPU užsakymus), galimybė perkelti dalį pakavimo darbo į kitą ekosistemą gali užtikrinti gamybos tęstinumą ir greitesnį išėjimą į rinką. Tai ypač svarbu duomenų centrams ir aukštos spartos skaičiavimo sprendimams, kur laikas iki rinkos gali tiesiogiai paveikti konkurencingumą.

Intel įvaizdį ir technologinį autoritetą taip pat sustiprina atviri pagyrimai: Nvidia generalinis direktorius Jensen Huang anksčiau viešai kalbėjo teigiamai apie Foveros, o tokios rekomendacijos suteikia papildomo patikimumo. Ar tai virstų reikšmingu komerciniu apimčiu, priklauso nuo kelių faktorių: gamybos sąnaudų, paklausos stabilumo, garantuotų tiekimo sutarčių ir nuo to, ar Intel sugebės užtikrinti konkurencingą laiką iki rinkos (time-to-market) ir pakavimo kokybę lyginant su ilgamečiais tiekėjais, tokiais kaip TSMC.

Be to, Intel pažangus pakavimas gali prasiskverbti į platesnį foundry paslaugų paketą — tiek per IDMs (Integrated Device Manufacturers) modelio plėtrą, tiek per trečiųjų šalių partnerystes. Tokios sinergijos gali atverti galimybes tiek dideliems technologiniams gigantams, tiek mažesnėms įmonėms, kurios ieško specializuotų paketų gamybos be priklausomybės nuo vienos tiekimo grandinės grandies.

Ką verta stebėti toliau

- Naujos partnerystės ar plokštelių (wafer) arba paketų lygio tiekimo sutartys tarp Intel ir didžiųjų dizainerių.

- Produktų dizainų paskelbimai, kurie aiškiai nurodo EMIB arba Foveros pakavimo sprendimus jų pakavimo užrašuose.

- TSMC talpos pokyčiai — bet kokie plėtra ar prioritetų pakeitimai greitai paveiks, kaip ir kada klientai pradės diversifikuotis.

Be šių punktų taip pat verta stebėti šiuos papildomus signalus: pirmuosius prototipų pavyzdžius arba bandymų projektus, kurie viešai dalins techninius duomenis apie EMIB/Foveros integracijos privalumus; pasikeitimus IP tiekimo grandinėse, kai tiekėjai pradės kurti chiplet-orientuotą IP; bei trečiųjų šalių pakavimo paslaugų teikėjų reakciją — ar jie pradės investuoti į panašias technologijas, kad neprarastų klientų.

Pažangus pakavimas tapo konkurencijos ašimi tiek, kiek ir proceso mazgai bei tranzistorių tankis. Intel EMIB ir Foveros nėra stebuklingi sprendimai, kurie išspręs visus lustų pramonės iššūkius, bet jie yra techniškai patikimos alternatyvos. Kai lustų gamintojai stumia našumo ribas kombinuodami chiplet’us ir sluoksniuotus die, inžineriniai įdarbinimai ir tylūs vertinimai dažnai išduoda didesnį strateginį poslinkį prieš komercinius paskelbimus. Sekite būsimus darbo skelbimus, partnerystės anonsus ir produktų išardymus (teardowns), kad sužinotumėte, ar Intel pakavimas taps pagrindiniu pasirinkimu kitai pritaikytų silicio bangai.

Techniniai aspektai, kuriuos verta laikyti požiūryje, apima terminio valdymo sprendimus, bandymo ir patikimumo procedūras chiplet architektūrose, testavimo metodikų adaptavimą prie sluoksniuotų die, ir tiekimo grandinės valdymo optimizavimą, kai dalys gaminamos skirtinguose proceso mazguose. Visa tai sudaro daugiapakopę inžinerinę, gamybinę ir verslo problematiką, kur sprendimus siūlančios įmonės turi pateikti ne tik technologijas, bet ir visapusišką palaikymą dizaino, testavimo ir masinės gamybos etapuose.

Šaltinis: wccftech

Komentarai

duompulsas

Wow, netikėtai, Intel EMIB/Foveros įeina į žaidimą. Jei pavyks sumažint TSMC spaudą, būtų stulbinimas. Bet thermal problemos, testai ir tiekimas, nemažai galvos skausmo

Tomas

Ar čia rimtai? Apple ir Qualcomm tyliai dairosi pas Intel, bet ar Intel talpa tikrai pajėgs? Gal tai tik prototipai, o ne masinė gamyba...

Palikite komentarą